# **USER GUIDE**

5 SLOT OPENVPX BACKPLANE BKP3-DIS05-15.2.13-3+

#### Copyright 2019 by Pixus Technologies Inc. All rights reserved.

No part of this manual, including the products and/or software described in it, may be reproduced, transmitted, transcribed, stored in any retrieval system, or translated in any language, in any form, or by any means—excluding documentation that is kept by the purchaser for backup purposes—without the express written permission of Pixus Technologies Inc.

Every effort has been made to ensure all information contained herein is accurate at the time of printing and is subject to change without notice and should not be construed as a commitment on the part of Pixus Technologies Inc. Neither Pixus Technologies, its employees, directors, officers, nor its agents are responsible for any damages, direct or consequential, to any and all equipment as a result of use of this product in a configured system.

All warranties expressed or implied are void if the product has (a) been repaired, damaged, modified, or altered in any way, unless such repair, modification or alterations are authorized in writing by Pixus Technologies Inc.; or (b) the serial number of the product is defaced or missing.

Products and corporate names appearing in this manual may or may not be registered trademarks or copyrights of their respective companies, and are used only for identification or explanation.

PICMG®, CompactPCI®, and the PICMG® and CompactPCI® logos are registered trademarks of the PCI Industrial Computer Manufacturer's Group.

Any changes or modifications to this product not expressly approved by the manufacturer could void any assurances of safety or performance.

#### **Contacting Us**

Pixus Technologies Inc. 50 Bathurst Drive, Unit 6 Waterloo, Ontario Canada N2V 2C5

(519) 885-5775

Visit our home page at <a href="www.pixustechnologies.com">www.pixustechnologies.com</a> for more information about Pixus products and services.

| Issue Date |             | Description     |  |

|------------|-------------|-----------------|--|

| 1.0        | 15-May-2019 | Product release |  |

# TYPOGRAPHICAL CONVENTIONS USED IN THIS DOCUMENT

| Items                                                                                           | Convention                                                                                                                                                         |  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| You will see the following icons periodically throughout this manual:                           |                                                                                                                                                                    |  |  |  |

|                                                                                                 | The <b>WARNING</b> icon cautions you against an action or treatment that could threaten the responsiveness of the equipment or the integrity of your current work. |  |  |  |

|                                                                                                 | The <b>INSPECT</b> icon alerts the reader to follow inspection instructions to ensure product is not damaged and in operational order.                             |  |  |  |

|                                                                                                 | The <b>NOTE</b> icon notifies you of the information that makes a procedure easier or clarifies an earlier description.                                            |  |  |  |

| Headings, titles, sections or words of importance.                                              | These items appear in <b>bold</b> typeface. Example: Any changes or modifications                                                                                  |  |  |  |

| Variable placeholders, references to other documents, new or special terminology, and emphasis. | These items appear in <i>italic</i> typeface. Example: Table 3-1, displays                                                                                         |  |  |  |

| References to chapters and sections of documents, and citations of messages displayed to users. | These items appear in "quotation marks." Example: For more information, refer to "Connections", section 3                                                          |  |  |  |

## **Revision History**

| Revision | Date        | Description                    | Author |

|----------|-------------|--------------------------------|--------|

| 1.0      | 15-May-2019 | Released for product approvals |        |

|          |             |                                |        |

|          |             |                                |        |

|          |             |                                |        |

|          |             |                                |        |

|          |             |                                |        |

|          |             |                                |        |

#### **TABLE OF CONTENTS**

| TYP | OGR/ | APHICAL CONVENTIONS USED IN THIS DOCUMENT    | 3  |

|-----|------|----------------------------------------------|----|

| SEC | TION | ONE                                          | 6  |

| 1.  |      | duction                                      |    |

|     |      | Pixus Technologies Inc.                      |    |

|     |      | Contact Information                          |    |

|     |      | Background Information                       |    |

|     |      | Applicability                                |    |

| SEC | TION | TWO                                          | 8  |

|     |      | tures                                        |    |

| SEC | TION | THREE                                        | 10 |

|     |      | k Start                                      |    |

|     |      | Inspecting Your Backplane                    |    |

|     | 3.2. | Installing Your Backplane In A Subrack       |    |

|     | 3.3. |                                              |    |

|     | 0.0. | 3.3.1. Miscellaneous Headers                 |    |

|     | 3.4. | Installing Plug-In Modules in Your Backplane |    |

| SEC |      | FOUR                                         |    |

|     |      |                                              |    |

| 4.  |      | erstanding Your Backplane                    |    |

|     |      | Backplane Connectors                         |    |

|     | 4.2. |                                              |    |

|     |      | 4.2.1. Vs1, Vs2, Vs3 and GND                 |    |

|     |      | 4.2.2. AUX Power                             |    |

|     |      | 4.2.3. Safety Ground                         |    |

|     | 4.2  | 4.2.4. Decoupling                            |    |

|     | 4.3. | Slot Identification                          |    |

|     |      | 4.3.1. Slot Keying                           |    |

|     | 11   | Backplane Topology                           |    |

|     |      | Backplane profile compatibility              |    |

|     |      | SYS CON*                                     |    |

|     |      | Control Plane                                |    |

|     |      | Expansion Plane                              |    |

|     |      | Data Plane                                   |    |

|     |      | . Connector Pinouts                          |    |

|     | 4.10 | 4.10.1. J0                                   |    |

|     |      | 4.10.2. J1                                   |    |

|     |      | 4.10.3. GDiscrete1                           |    |

|     |      | 4.10.4. SYS CON*                             |    |

|     |      | 4.10.5. UD                                   |    |

|     |      | 4.10.6. MaskableReset*                       |    |

|     |      | 4.10.7. P1-VBAT                              |    |

|     |      | 4.10.8. J2                                   |    |

|     | 4.11 | . Regulatory and Safety                      | 24 |

| SEC | TION | FIVE                                         | 25 |

|     |      | endiv A                                      | 25 |

| 5.1. Acronyms                                         |    |

|-------------------------------------------------------|----|

| 5.2. Torque Values                                    | 26 |

| 5.3. List of Connectors                               |    |

|                                                       |    |

| LICT OF FIGURES                                       |    |

| LIST OF FIGURES Figure 2-1: Connector Locations       | 0  |

|                                                       |    |

| Figure 3-1: Digital Ground – Chassis Ground Tie Point |    |

| Figure 4-1: Backplane Topology                        |    |

| Figure 4-2 SM Bus Terminations                        | 21 |

|                                                       |    |

| LIST OF TABLES                                        |    |

| Table 1-1: Applicability                              | 7  |

| Table 1-1: Applicability                              |    |

|                                                       |    |

| Table 3-2: VBAT Connector Pinout                      |    |

| Table 3-3: System Management Connectors               |    |

| Table 4-1: AUX Power Connections                      |    |

| Table 4-2 Slot Keying                                 |    |

| Table 4-3 Geographic Addressing                       |    |

| Table 4-4: Backplane Profile Compatibility            |    |

| Table 4-5 Data Plane Port Allocation                  |    |

| Table 4-6 J0 Pin Assignment                           |    |

| Table 4-7 SM Bus Termination Resistor Mapping         |    |

| Table 4-8 Payload J1 Pin Assignment                   |    |

| Table 4-9 Peripheral J1 Pin Assignment                |    |

| Table 4-10 J2 Pin Assignment                          |    |

| Table 5-1: Recommended Torque Values                  |    |

| Table 5-2: Backplane Connectors                       | 27 |

## SECTION ONE

## 1. INTRODUCTION

This section provides a brief overview about Pixus Technologies Inc. This section describes the following:

- 1.1 Pixus Technologies Inc.

- 1.2 Contact Information

- 1.3 Background Information

- 1.4 Applicability

#### 1.1. PIXUS TECHNOLOGIES INC.

Pixus Technologies specializes in the design and manufacture of electronic packaging solutions for the global embedded computer market. The company is comprised of three business units: backplanes, Enclosure & System Solutions and Components.

Leveraging over 20 years of innovative product development, Pixus Technologies' embedded backplanes and systems are focused primarily on xTCA, OpenVPX, CompactPCI, PCIe and custom designs. The company offers unsurpassed thermal management solutions, creative design innovations, and backplane design expertise. Pixus also offers modular 19" rackmount enclosure solutions and instrument cases to a wide range of industries, as well as precision components such as front panels, handles, and card guides.

The approach to each customer requirement is a simple consultative philosophy - understand the specific program requirements and create the best solution that meets the time frame, architecture, technology and cost objectives.

#### 1.2. CONTACT INFORMATION

For questions about the Pixus product or about Pixus in general, please contact us using the following information:

**Phone Number:** (519) 885-5775 **Fax Number:** (226) 444-0225

Web Address: <a href="https://www.pixustechnologies.com">www.pixustechnologies.com</a>

<a href="https://www.pixustechnologies.com">Mailing Address:</a>

<a href="https://www.pixustechnologies.com">Pixus Technologies.com</a>

<a href="https://www.pixustechnologies.com">Pixus Technologies.com</a>

50 Bathurst Drive, Unit 6

Waterloo, Ontario

Canada N2V 2C5

For Pixus product support, see the Pixus web site: www.pixustechnologies.com

#### 1.3. BACKGROUND INFORMATION

When designing OpenVPX® systems, use the following documents for reference:

- ANSI/VITA® 62.0 Modular Power Supply Standard

- ANSI/VITA® 48.0 Mechanical Specification for Microcomputers Using Ruggedized Enhanced Design Implementation (REDI)

- ANSI/VITA® 48.1 Mechanical Specification for Microcomputers Using REDI Air Cooling

- ANSI/VITA® 46.0-2007 VPX Baseline Standard

- ANSI/VITA® 46.1-2007 VMEbus Signal Mapping on VPX

- ANSI/VITA® 46.3-2012 Serial RapidIO® on VPX Fabric Connector

- ANSI/VITA® 46.4-2012 PCI Express® on VPX Fabric Connector

- ANSI/VITA® 46.6-2013 Gigabit Ethernet Control Plane on VPX

- ANSI/VITA® 46.7-2012 Ethernet on VPX Fabric Connector

- ANSI/VITA® 46.8-VDSTU Infiniband® on the VPX Fabric Connector

- ANSI/VITA® 46.9-2010 PMC/XMC Rear I/I Signal Mapping on 3U and 6U VPX Module

- ANSI/VITA® 46.10-2009 Rear Transition Module for VPX

- ANSI/VITA® 46.11-VDSTU System Management for VPX

- ANSI/VITA® 46.9 PMC/XMC Rear I/O Fabric Signal Mapping on 3U and 6U VPX Modules Standard

- ANSI/VITA® 65.0-2017 OpenVPX® System Standard

- ANSI/VITA® 65.1-2017 OpenVPX® System Standard Profile Tables

- ANSI/VITA® 68.0-VDSTU VPX Compliance Channel

- ANSI/VITA® 68.1-VDSTU VPX Compliance Channel Fixed Signal Integrity Budget

- RoHS 2011/65/EU

#### 1.4. APPLICABILITY

This User Guide is applicable to the following model(s):

| Model               | Description                                          |

|---------------------|------------------------------------------------------|

| VPX30-05-XX-12A41-0 | 3U 5 Slot OpenVPX Backplane Power/Ground w RTM       |

| VPX30-05-XX-12X41-0 | 3U 5 Slot OpenVPX Backplane Power/Ground w/o RTM     |

| VPX30-05-XX-12C41-0 | 3U 5 Slot OpenVPX Backplane Power/Ground Partial RTM |

|                     |                                                      |

Table 1-1: Applicability

## SECTION TWO

## 2. FEATURES

The backplane has been designed with the following features:

- Conformance to VITA 65.x BKP3-DIS05-15.2.13-3+ profile.

- Support for 5 3U 5HP Modules.

- 8Gbps minimum signaling rate.

- ANSI/VITA® 65.0 and 65.1 compliant.

- Mechanical conformance to 132mm W x 128.7mm H x 5.4mm T.

- Eighteen layer construction.

- Power elements for primary power input.

- Individual 5-pin headers for JTAG connectivity at each slot.

- Two 8-pin headers for access to the system management bus and control signals.

- Support for 5 rear I/O Modules.

- Peripheral slots conform to VITA 65.1 SLT3-PER-1F-14.3.2 profile.

- Payload slots conform to VITA 65.1 SLT3-PAY-2F-14.2.7 profile.

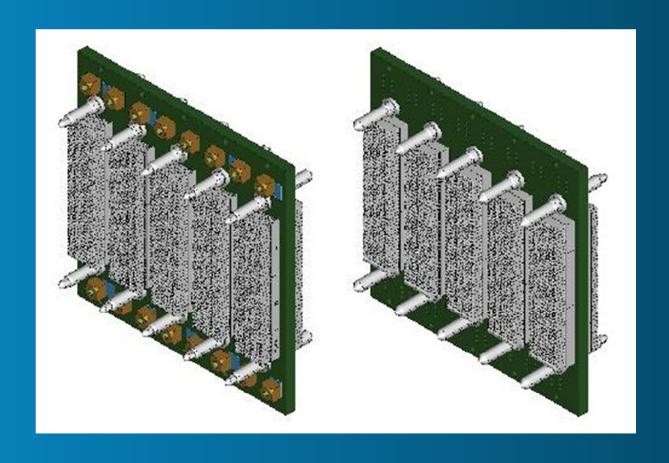

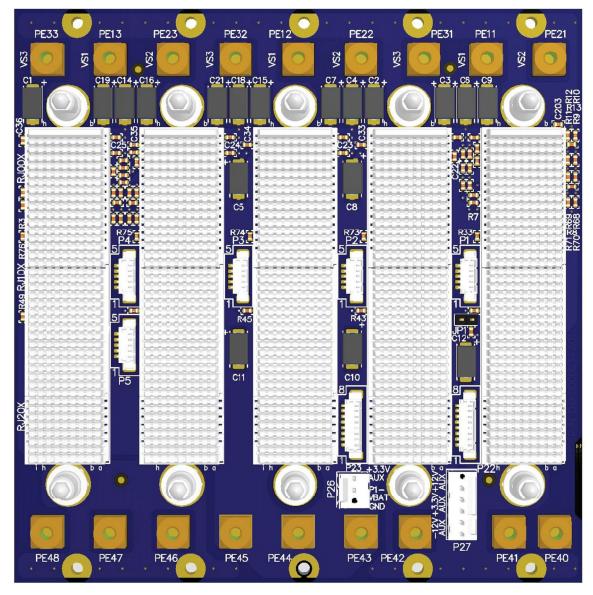

Figure 2-1 illustrates the major features of the backplane, showing approximate locations for all connectors.

Figure 2-1: Connector Locations

## SECTION THREE

## 3. QUICK START

The backplane complies with the VITA standards as they were when the backplane was created.

This chapter will provide an overview of basic operating procedures, including the following:

- Inspecting Your Backplane

- Installing Your Backplane In A Subrack

- Accessory Connections

#### 3.1. INSPECTING YOUR BACKPLANE

Take great care when handling the backplane. Improper handling could cause damage to the connector pins.

Always handle the backplane from the edges, never the connectors.

The first item that must be done before starting to utilize your backplane is to perform a thorough inspection.

During the course of handling, shipping and assembly, pins, mounting screws and other items could become damaged and/or loose. Operating a damaged backplane could cause serious damage to the backplane and/or devices that interface to it.

Take a few minutes to visually inspect that all of the connector pins are straight, screws are tight, etc.

Repair any bent pins, loose screws, etc. before proceeding. If damage to the backplane is deemed too extensive, call Pixus Customer Service for assistance on how to proceed.

#### 3.2. INSTALLING YOUR BACKPLANE IN A SUBRACK

The backplane mounts into a sub-rack using M2.5 screws along the rows of mounting holes situated at the top and bottom end of each slot, with all mounting holes connecting to chassis ground with the possible exception of one.

The mounting rail areas of the backplane have exposed strips of copper that are connected directly to the chassis ground of the backplane.

The backplane must be mounted in the sub-rack with insulator strips between it and the rails. Applications where conductive strips are utilized must be inspected to make sure there is no electrical contact between the rails and any device on the backplane.

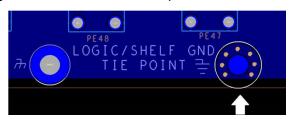

As stated above, there is possibly one mounting screw that allows digital ground to be tied to chassis (frame) ground. The mounting hole that connects to digital ground is marked with the corresponding symbol (=) on the bottom silkscreen.

The arrow in Figure 3-1 illustrates the screw location for the single ground tie point.

Refer to the subrack user guide for information on torque limits for the mounting screws.

Figure 3-1: Digital Ground – Chassis Ground Tie Point

## 3.3. ACCESSORY CONNECTIONS

#### 3.3.1. MISCELLANEOUS HEADERS

#### 3.3.1.1. JTAG

Each slot has a 5 pin header (P1-5]) to allow access to the slot's JTAG signals.

Refer to Table 5-2 for a suitable mating connector and wire crimps.

Table 3-1 displays the pinout for the JTAG headers along with the corresponding pin on the slot

| Pin # | Signal Backplane Pin |             |

|-------|----------------------|-------------|

| 1     | TRST_[1:5]           | J0[01:5] a7 |

| 2     | TMS_[1:5]            | J0[01:5] b7 |

| 3     | TDI_[1:5]            | J0[01:5] e7 |

| 4     | TDO_[1:5]            | J0[01:5] f7 |

| 5     | TCK_[1:5]            | J0[01:5] i7 |

Table 3-1: JTAG Connectors

#### 3.3.1.2. VBAT

One 3-pin header (P26) is supplied on the rear side for external connection to VBAT and 3.3V\_AUX.

A standard 0.100" shunt is provided to connect VBAT to either GND or 3.3V\_AUX. By default, the connection is to 3.3V\_AUX.

Refer to Table 5-2 for a suitable mating connector and wire crimps for other applications.

Table 3-2 illustrates the pinout for the VBAT connector.

| Pin# | Signal   |                   |

|------|----------|-------------------|

| 1    | GND      |                   |

| 2    | VBAT     |                   |

| 3    | 3.3V_AUX | ₩ ₩ ₩<br><b>1</b> |

Table 3-2: VBAT Connector Pinout

#### 3.3.1.3. System Management

There are two 8 pin headers (P22, P23) to allow access to the System Management signals.

Refer to Table 5-2 for a suitable mating connector and wire crimps.

Table 3-3 on page 12 displays the pinout for the System Management headers.

| Pin # | Signal (P22)      | Signal (P23) |

|-------|-------------------|--------------|

| 8     | SM1               | SM3          |

| 7     | SM0               | SM2          |

| 6     | SYSRESET*         | SYSRESET*    |

| 5     | GND GND           |              |

| 4     | NVMRO NVMRO       |              |

| 3     | MSK_RST* MSK_RST* |              |

| 2     | 2 GND GND         |              |

| 1     | 3.3V_AUX          | 3.3V_AUX     |

Table 3-3: System Management Connectors

Note that MSK\_RST\* is only present on these pins when it is bussed to all slots.

#### 3.3.1.4. NVMRO

The backplane busses this signal to all slots.

Jumper JP1 allows for the signal to be grounded on the backplane.

#### 3.4. INSTALLING PLUG-IN MODULES IN YOUR BACKPLANE

The backplane supports up to 5 OpenVPX® Plug-In Modules.

Refer to section 4.3 for information on which Plug-In Module goes into which slot.

The latching/unlatching mechanism on the Plug-In Module should suffice for insertion/extraction.

Do not use excessive force when installing or removing Plug-In Modules from the chassis. Use of excessive force can result in damage to the backplane and/or Plug-In Module. Should excessive force be required, remove the Plug-In Module(s) and verify the alignment of the mechanicals and backplane.

There is no preset order to inserting Plug-In Modules into the backplane. Refer to the Plug-In Module and/or chassis User Manual(s) for more information on inserting Plug-In Modules.

## SECTION FOUR

## 4. UNDERSTANDING YOUR BACKPLANE

#### 4.1. BACKPLANE CONNECTORS

The complete list of connectors utilized on the backplane is listed in Table 5-2.

#### 4.2. POWER CONNECTORS

Slots are powered through power elements and for lower slot count backplanes, a combination of power elements and a header. The backplane distributes DC power (12V, 5V, 3.3V, 3.3V\_AUX, +12V AUX & -12V AUX) to each slot through the internal copper planes.

The power elements are capable of providing 60 Amps in a 70° C ambient environment.

The AUX power connector (P27) for the narrower backplanes is rated at 4 Amps per pin. There is no derating information available.

#### 4.2.1. VS1, VS2, VS3 AND GND

Per the specification, each slot can source 22A on Vs1, Vs2 and Vs3.

The Vs1, Vs2 and Vs3 power elements (as applicable) are on the top rear of the backplane.

Vs1 power elements are referenced from PE11-PE17 and are bused on the backplane.

Vs2 power elements are referenced from PE21-PE27 and are bused on the backplane.

Vs3 power elements are referenced from PE31-PE37 and are bused on the backplane.

There is one corresponding GND power element for each Vs[1-3] power element. GND power elements are on the lower rear of the backplane.

Ground power elements are referenced from PE40-PE60 and are bussed on the backplane.

#### 4.2.2. AUX POWER

Per the specification, each slot can source 1A on 3.3V AUX, +12V AUX and -12V AUX.

Where space permits, this is done with power elements. If present, these will be located on the top rear of the backplane.

Where space does not permit, it is done with a PCB-wire header (P27).

Refer to Table 5-2 for a suitable mating connector and wire crimps. Table 4-1 provides the pinout for the AUX power connections.

| Pin# | Signal   | Signal |  |  |

|------|----------|--------|--|--|

| 1    | +12V_AUX | DE71   |  |  |

| 2    | +12V_AUX | - PE71 |  |  |

| 3    | 3.3V_AUX | PE72   |  |  |

| 4    | 3.3V_AUX |        |  |  |

| 5    | -12V_AUX | PE73   |  |  |

| 6    | -12V_AUX |        |  |  |

Table 4-1: AUX Power Connections

#### 4.2.3. SAFETY GROUND

The top and bottom mounting rail surfaces are the connection point to safety ground.

The alignment keys each have a minimum 20 A path to the connection point.

Some backplanes will have a feature for allowing safety ground to be tied to logic ground. Refer to section 3.2.

#### 4.2.4. DECOUPLING

Each slot has provisions for decoupling capacitors.

A high frequency decoupling capacitor (0.1 uf) is provided for each power rail at each slot.

Provisions for optional bulk filtering capacitors are provided for each power rail at each slot. These can be requested as an option when noisy power rails are expected.

#### 4.3. SLOT IDENTIFICATION

#### 4.3.1. SLOT KEYING

3U backplanes have 2 alignment/keying devices as required in the ANSI/VITA 46.0 specification.

6U backplanes have 3 alignment/keying devices as required in the ANSI/VITA 46.0 specification.

Table 4-2 provides the as-shipped keying settings for 3U and 6U backplanes.

| Slot# | 3     | U     |       | 6U    |       |

|-------|-------|-------|-------|-------|-------|

|       | Key 1 | Key 2 | Key 1 | Key 2 | Key 3 |

| 1     | 270°  | 270°  | 315°  | 270°  | 270°  |

| 2     | 315°  | 270°  | 315°  | 315°  | 270°  |

| 3     | 0°    | 270°  | 315°  | 0°    | 270°  |

| 4     | 45°   | 270°  | 315°  | 45°   | 270°  |

| 5     | 90°   | 270°  | 315°  | 90°   | 270°  |

| 6     | 270°  | 315°  | 315°  | 270°  | 315°  |

| 7     | 315°  | 315°  | 315°  | 315°  | 315°  |

| 8     | 0°    | 315°  | 315°  | 0°    | 315°  |

| 9     | 45°   | 315°  | 315°  | 45°   | 315°  |

| 10    | 90°   | 315°  | 315°  | 90°   | 315°  |

| Slot# | 3U    |       | 6U    |       |       |

|-------|-------|-------|-------|-------|-------|

|       | Key 1 | Key 2 | Key 1 | Key 2 | Key 3 |

| 11    | 270°  | 0°    | 315°  | 270°  | 0°    |

| 12    | 315°  | 0°    | 315°  | 315°  | 0°    |

| 13    | 0°    | 0°    | 315°  | 0°    | 0°    |

| 14    | 45°   | 0°    | 315°  | 45°   | 0°    |

| 15    | 90°   | 0°    | 315°  | 90°   | 0°    |

| 16    | 270°  | 45°   | 315°  | 270°  | 45°   |

| 17    | 315°  | 45°   | 315°  | 315°  | 45°   |

| 18    | 0°    | 45°   | 315°  | 0°    | 45°   |

| 19    | 45°   | 45°   | 315°  | 45°   | 45°   |

| 20    | 90°   | 45°   | 315°  | 90°   | 45°   |

| 21    | 270°  | 90°   | 315°  | 270°  | 90°   |

Table 4-2 Slot Keying

#### 4.3.2. SLOT NUMBERING

Slots are numbered according to the ANSI/VITA 46 specification.

The leftmost slot (viewed from the front) always has a geographic address of 1 and will increment by one.

Table 4-3 illustrates the slot geographic address on the various length backplanes.

| Slot# | GAP* | GA4* | GA3* | GA2* | GA1* | GA0* |

|-------|------|------|------|------|------|------|

| 1     | Open | Open | Open | Open | Open | GND  |

| 2     | Open | Open | Open | Open | GND  | Open |

| 3     | GND  | Open | Open | Open | GND  | GND  |

| 4     | Open | Open | Open | GND  | Open | Open |

| 5     | GND  | Open | Open | GND  | Open | GND  |

| 6     | GND  | Open | Open | GND  | GND  | Open |

| 7     | Open | Open | Open | GND  | GND  | GND  |

| 8     | Open | Open | GND  | Open | Open | Open |

| 9     | GND  | Open | GND  | Open | Open | GND  |

| 10    | GND  | Open | GND  | Open | GND  | Open |

| 11    | Open | Open | GND  | Open | GND  | GND  |

| 12    | GND  | Open | GND  | GND  | Open | Open |

| 13    | Open | Open | GND  | GND  | Open | GND  |

| 14    | Open | Open | GND  | GND  | GND  | Open |

| 15    | GND  | Open | GND  | GND  | GND  | GND  |

| 16    | Open | GND  | Open | Open | Open | Open |

| 17    | GND  | GND  | Open | Open | Open | GND  |

| 18    | GND  | GND  | Open | Open | GND  | Open |

| Slot# | GAP* | GA4* | GA3* | GA2* | GA1* | GA0* |

|-------|------|------|------|------|------|------|

| 19    | Open | GND  | Open | Open | GND  | GND  |

| 20    | GND  | GND  | Open | GND  | Open | Open |

| 21    | Open | GND  | Open | GND  | Open | GND  |

Table 4-3 Geographic Addressing

#### 4.4. BACKPLANE TOPOLOGY

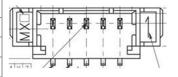

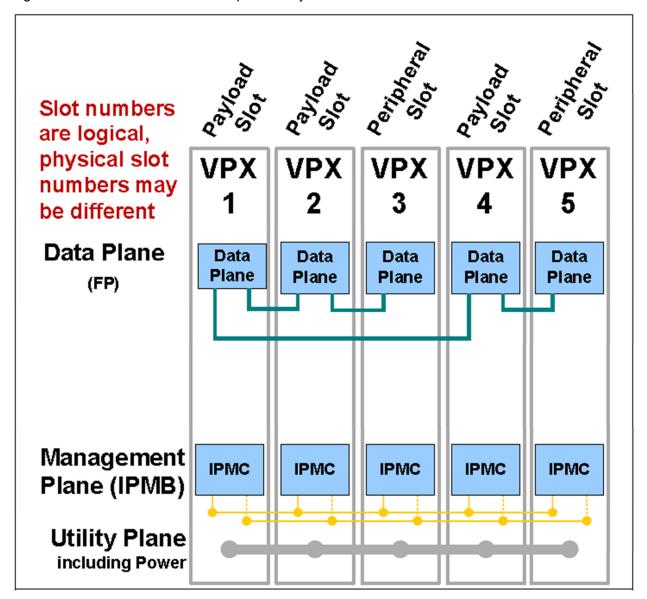

Figure 4-1 illustrates the backplane topology. The dotted lines from the Payload and Switch slots are signals that are available to the complementary RTM.

Figure 4-1: Backplane Topology

## 4.5. BACKPLANE PROFILE COMPATIBILITY

Table 4-4 displays the list of Backplane Profiles that the backplane is compatible with.

Slot profile information is also provided.

A "+" at the end of the profile name indicates that this particular profile was not approved as part of ANSI/VITA 65.1 at the time of publication of this document.

| 1                             |                             |                          |  |  |

|-------------------------------|-----------------------------|--------------------------|--|--|

| Control and Data Plane Switch | Slot Profile                | SLT3-PER-1F-14.3.2       |  |  |

| Cor                           | Slot(s)                     | 3,5                      |  |  |

| Payload                       | Slot Profile                | SLT3-PAY-2F-14.2.7       |  |  |

|                               | Slot(s)                     | 1,2,4                    |  |  |

|                               |                             |                          |  |  |

| Channel Gbaud Rate            | Expansion<br>Plane<br>(DFP) |                          |  |  |

| Channel G                     | Data<br>Plane<br>(FP)       | 8                        |  |  |

|                               | Control<br>Plane<br>(UTP)   |                          |  |  |

| ical                          | RTM                         | 46.10                    |  |  |

| Mechanical Pitch R1 (in) co   |                             | BKP3-DIS05-15.2.13-3 1.0 |  |  |

| Backylane Drefile Names       | Backplane Profile Names     |                          |  |  |

Table 4-4: Backplane Profile Compatibility

## 4.6. SYS\_CON\*

This signal is pulled low on physical slot 1.

Each slot has the option of having this signal pulled low.

Consult Pixus Technologies for information on how this can be accomplished.

#### 4.7. CONTROL PLANE

The backplane has no control plane.

### 4.8. EXPANSION PLANE

The backplane has no expansion plane.

#### 4.9. DATA PLANE

The backplane has the Data Plane Ports connected as shown in Table 4-5.

Dotted lines are signals that are available to the adjacent RTM.

| Slot/Channel | DP01       | DP02       |

|--------------|------------|------------|

| 1            | VPX02-DP01 | VPX04-DP01 |

| 2            | VPX01-DP01 | VPX03-DP01 |

| 3            | VPX02-DP02 |            |

| 4            | VPX01-DP02 | VPX05-DP01 |

| 5            | VPX04-DP02 |            |

Table 4-5 Data Plane Port Allocation

#### 4.10. CONNECTOR PINOUTS

#### 4.10.1. J0

Table 4-6 defines the signals present on J0 for all slots.

|   | Row i | Row h    | Row g    | Row f | Row e    | Row d    | Row c     | Row b | Row a |

|---|-------|----------|----------|-------|----------|----------|-----------|-------|-------|

| 1 | Vs1   | Vs1      | Vs1      | Vs1   | No Pad*  | Vs2      | Vs2       | Vs2   | Vs2   |

| 2 | Vs1   | Vs1      | Vs1      | Vs1   | No Pad*  | Vs2      | Vs2       | Vs2   | Vs2   |

| 3 | Vs3   | Vs3      | Vs3      | Vs3   | No Pad*  | Vs3      | Vs3       | Vs3   | Vs3   |

| 4 | GND   | SM2      | SM3      | GND   | -12V_Aux | GND      | SYSRESET* | NVMRO | GND   |

| 5 | GND   | GAP*     | GA4*     | GND   | 3.3V_Aux | GND      | SM0       | SM1   | GND   |

| 6 | GND   | GA3*     | GA2*     | GND   | +12V_Aux | GND      | GA1*      | GA0*  | GND   |

| 7 | тск   | GND      | GND      | TDO   | TDI      | GND      | GND       | TMS   | TRST* |

| 8 | GND   | REF_CLK- | REF_CLK+ | GND   | GND      | AUX_CLK- | AUX_CLK+  | GND   | GND   |

Table 4-6 J0 Pin Assignment

#### 4.10.1.1. REF/AUX\_CLK

These are bussed differential pairs with an impedance of 130 Ohms +-10%, terminated with 61.9 Ohm +-1% resistors.

#### 4.10.1.2. System Management

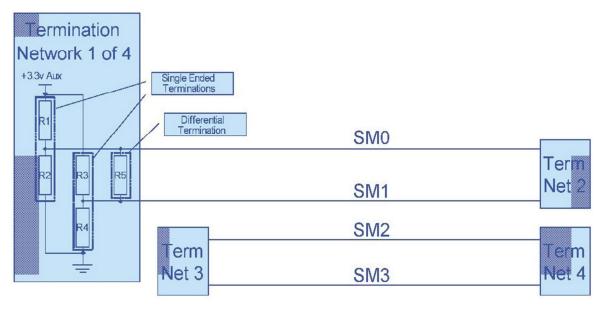

These signals are bused to all slots with facilities for single-ended and differential termination at both ends of the signals.

When configured for IPMB operation, each signal must be pulled high to 3.3V\_AUX by a 2k49 Ohm +-1% resistor at one end only.

Figure 4-2 illustrates the termination resistor configuration for the System Management bus.

Table 4-7 provides the mapping for the SM Bus termination resistor pairs (Term1/Term2 and Term3/Term4). Note that the resistor sites are all 0603 sized.

| Signal | R1      | R2      | R3      | R4      | R5      |

|--------|---------|---------|---------|---------|---------|

| SM0    | R40/R11 | R41/R12 |         |         | R50/R13 |

| SM1    |         |         | R38/R9  | R39/R10 | R50/R13 |

| SM2    | R53/R16 | R54/R17 |         |         | R55/R18 |

| SM3    |         |         | R51/R14 | R52/R15 | R55/R18 |

Table 4-7 SM Bus Termination Resistor Mapping

Figure 4-2 SM Bus Terminations

#### 4.10.1.3. NVMRO

This signal is bussed to all slots.

Jumper JP1 allows for the signal to be grounded on the backplane.

#### 4.10.1.4. SYSRESET\*

This signal is bussed to all slots and is pulled high to 3.3V\_AUX by a 220 Ohm +-5% resistor and pulled low by a 1k8 Ohm +-5% resistor.

#### 4.10.2. J1

Table 4-8 and Table 4-9 provide the pin assignments for J1 on the Payload and Peripheral slots.

#### **4.10.3. GDISCRETE1**

The backplane busses this signal to all slots.

The single-ended impedance is 50 Ohms.

470 Ohm +-5% resistors terminate the signal at both end of the backplane to 3.3V\_AUX.

#### 4.10.4. SYS\_CON\*

Slot number 1 (leftmost) has this pin connected to ground.

All slots have provision for connecting this pin to ground.

#### 4.10.5. UD

These pins are application specific and not defined.

#### 4.10.6. MASKABLERESET\*

This pin is application specific and not defined. The backplane busses the signal and routes it to P22 and P23.

#### 4.10.7. P1-VBAT

The backplane busses this signal to all slots and to P26. Refer to Section 3.3.1.2.

| Plug- | ln                   | Row G              | Row F     | Ro        | wΕ       | Row D    | Row C    | Ro       | мB       | Row A    |

|-------|----------------------|--------------------|-----------|-----------|----------|----------|----------|----------|----------|----------|

| Modu  | le P1                |                    |           | Even      | Odd      |          |          | Even     | Odd      |          |

| Bplan | ie J1                | Row i              | Row h     | Row g     | Rowf     | Row e    | Row d    | Row c    | Rowb     | Row a    |

| 1     | ω.                   | GD iscrete1        | GND       | GND-J1    | DP01-T0- | DP01-T0+ | GND      | GND-J1   | DP01-R0- | DP01-R0+ |

| 2     | lan<br>t 1           | GND                | DP 01-T1- | DP 01-T1+ | GND-J1   | GND      | DP01-R1- | DP01-R1+ | GND-J1   | GND      |

| 3     | ata Plane<br>Port 1  | P1-VBAT            | GND       | GND-J1    | DP01-T2- | DP01-T2+ | GND      | GND-J1   | DP01-R2- | DP01-R2+ |

| 4     | ä                    | GND                | DP 01-T3- | DP 01-T3+ | GND-J1   | GND      | DP01-R3- | DP01-R3+ | GND-M    | GND      |

| 5     | 0                    | SYS_CON*           | GND       | GND-J1    | DP02-T0- | DP02-T0+ | GND      | GND-J1   | DP02-R0- | DP02-R0+ |

| 6     | t 2                  | GND                | DP 02-T1- | DP 02-T1+ | GND-J1   | GND      | DP02-R1- | DP02-R1+ | GND-J1   | GND      |

| 7     | Data Plane<br>Port 2 | Reserved           | GND       | GND-J1    | DP02-T2- | DP02-T2+ | GND      | GND-J1   | DP02-R2- | DP02-R2+ |

| 8     |                      | GND                | DP 02-T3- | DP 02-T3+ | GND-J1   | GND      | DP02-R3- | DP02-R3+ | GND-M    | GND      |

| 9     |                      | UD                 | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 10    | 1                    | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | GND-J1   | GND      |

| 11    | ا پا                 | UD                 | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 12    | User Defined         | GND                | UD        | UD        | GNDJ1    | GND      | UD       | UD       | GND-M    | GND      |

| 13    | g D                  | UD                 | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 14    | °                    | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | GND-J1   | GND      |

| 15    |                      | Maskable<br>Reset* | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 16    |                      | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | GND-J1   | GND      |

Table 4-8 Payload J1 Pin Assignment

| Plug-l | n                    | Row G              | Row F     | Ro        | wΕ       | Row D    | Row C    | Ros      | wВ       | Row A    |

|--------|----------------------|--------------------|-----------|-----------|----------|----------|----------|----------|----------|----------|

| Modu   | le P1                |                    |           | Even      | Odd      |          |          | Even     | Odd      |          |

| Bplan  | e J1                 | Row i              | Row h     | Row g     | Row f    | Row e    | Row d    | Row c    | Rowb     | Row a    |

| 1      | 0                    | GD iscrete1        | GND       | GND-J1    | DP01-T0- | DP01-T0+ | GND      | GND-J1   | DP01-R0- | DP01-R0+ |

| 2      | t 1                  | GND                | DP 01-T1- | DP 01-T1+ | GND-J1   | GND      | DP01-R1- | DP01-R1+ | G ND-M   | GND      |

| 3      | Data Plane<br>Port 1 | P1-VBAT            | GND       | GND-J1    | DP01-T2- | DP01-T2+ | GND      | GND-J1   | DP01-R2- | DP01-R2+ |

| 4      | a                    | GND                | DP 01-T3- | DP 01-T3+ | GND-J1   | GND      | DP01-R3- | DP01-R3+ | G ND-J1  | GND      |

| 5      |                      | SYS_CON*           | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 6      |                      | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | G ND-M   | GND      |

| 7      |                      | Reserved           | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 8      |                      | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | G ND-M   | GND      |

| 9      | -                    | UD                 | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 10     | Defined              | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | G ND-J1  | GND      |

| 11     | er De                | UD                 | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 12     | User                 | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | G ND-J1  | GND      |

| 13     |                      | UD                 | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 14     |                      | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | G ND-J1  | GND      |

| 15     |                      | Maskable<br>Reset* | GND       | GND-J1    | UD       | UD       | GND      | GND-J1   | UD       | UD       |

| 16     |                      | GND                | UD        | UD        | GND-J1   | GND      | UD       | UD       | GND-J1   | GND      |

Table 4-9 Peripheral J1 Pin Assignment

#### 4.10.8. J2

Table 4-10 provides the pin assignments for J2 all slots. Note that these are strictly pass-through to the associated RTMs.

| Backplane<br>Jn | Row i | Row h | Row g | Row f | Row e | Row d | Row c | Row b | Row a |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 1               | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 2               | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

| 3               | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 4               | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

| 5               | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 6               | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

| 7               | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 8               | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

| 9               | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 10              | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

| 11              | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 12              | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

| 13              | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 14              | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

| 15              | UD    | UD    | UD    | UD    | UD    | GND   | UD    | UD    | UD    |

| 16              | GND   | UD    | UD    | GND   | UD    | UD    | UD    | UD    | GND   |

Table 4-10 J2 Pin Assignment

## 4.11. REGULATORY AND SAFETY

The backplanes have been designed to comply with the following standards:

- EN 69050

- UL 1950

A clearance of 2.5 mm has been provided between AC voltages and chassis ground on all external layers. A clearance of 5 mm has been provided between AC and secondary voltages on all internal layers. A clearance of 0.4 mm has been provided between primary and secondary voltages on all internal layers.

# SECTION FIVE

## 5. APPENDIX A

## 5.1. ACRONYMS

The following list provides definitions of acronyms used throughout this document.

| ACRONYM          | DEFINITION                                                                                                                                                                               |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 HP             | The width of a typical single width OpenVPX Slot. The distance between adjacent 5HP slots is exactly 1.00"                                                                               |

| 84HP             | This is the typical maximum width of a 14 slot backplane. The mechanical drawings should be used for exact dimensions and backplane mounting screw locations.                            |

| ATR              | Air Transport Rack                                                                                                                                                                       |

| BP               | Backplane                                                                                                                                                                                |

| ChMC             | Chassis Management Controller. An IPMC that is also capable of supporting the functions required of the Chassis Manager.                                                                 |

| ECN              | Engineering Change Notice                                                                                                                                                                |

| EMC              | Electromagnetic Compatibility                                                                                                                                                            |

| ESD              | Electrostatic Discharge                                                                                                                                                                  |

| FCC              | Federal Communications Commission                                                                                                                                                        |

| FE               | Fast Ethernet (10/100)                                                                                                                                                                   |

| FRU              | Field Replaceable Unit                                                                                                                                                                   |

| GA               | Geographical Addressing                                                                                                                                                                  |

| GE               | Gigabit Ethernet (1000)                                                                                                                                                                  |

| GPIO             | General Purpose Input Output                                                                                                                                                             |

| HP               | Horizontal Pitch (aperture width) 5.08mm (0.2")                                                                                                                                          |

| I/O              | Input/Output                                                                                                                                                                             |

| I <sup>2</sup> C | Intelligent Interface Controller                                                                                                                                                         |

| IPMB             | Intelligent Platform Management Bus                                                                                                                                                      |

| IPMC             | Intelligent Platform Management Controller. The portiong of a Field Replaceable Unit (FRU) that interfaces to the OpenVPX IPMB-0 and represent that FRU and any device subsidiary to ti. |

| LVDS             | Low Voltage Differential Signal                                                                                                                                                          |

| N/C              | Not Connected                                                                                                                                                                            |

| P/N              | Part Number                                                                                                                                                                              |

| PCB              | Printed Circuit Board                                                                                                                                                                    |

| PCI              | Peripheral Component Interconnect                                                                                                                                                        |

| PWM              | Pulse Width Modulation                                                                                                                                                                   |

| SBC              | Single Board Computer                                                                                                                                                                    |

| SMB              | System Management Bus                                                                                                                                                                    |

| SMD              | System Management Device                                                                                                                                                                 |

| ACRONYM | DEFINITION                             |

|---------|----------------------------------------|

| U       | Unit (vertical height) 44.45mm (1.75") |

| UL      | Underwriter's Laboratory               |

| V(I/O)  | Voltage (Input/Output)                 |

| VPX     | VME PCI X                              |

|         |                                        |

|         |                                        |

|         |                                        |

## 5.2. TORQUE VALUES

Table 5-1 displays the recommended torque values for fasteners used on the backplanes.

| Screws             | Torque               |

|--------------------|----------------------|

| Power Element (M3) | 0.5 Nm (4.43 lbf.in) |

| Keyed Guide Pin    | 0.45 Nm (4 in-lb)    |

|                    |                      |

Table 5-1: Recommended Torque Values

## 5.3. LIST OF CONNECTORS

Table 5-2 displays the list of connectors utilized on the backplane.

| Description                                      | Reference                                        | Vendor         | Conn. P/N                    | Rating | Mating Conn. P/N |

|--------------------------------------------------|--------------------------------------------------|----------------|------------------------------|--------|------------------|

| Power Elements                                   | PE11-PE13<br>PE21-PE22<br>PE31-PE33<br>PE40-PE47 | ERNI/<br>Wurth | 225693/7461057               | 94V-0  |                  |

| Management 1x8                                   | P22, P23                                         | Molex          | 53398-0871                   | 94V-0  | 51021-0800       |

| JTAG Connector                                   | P1-P5                                            | Molex          | 53398-0571                   | 94V-0  | 51021-0500       |

| MultiGig Keyed<br>Guide Pin 24mm<br>3.6-7.5mm    | K1[01-05]<br>K2[01-05]                           | TE             | 1410956-1                    | 94V-0  |                  |

| MultiGig RT T2.8"<br>Half Left                   | J0[01-05]<br>RJ2[01-05]                          | TE/ept         | 1410186-2 / 308-<br>52200-42 | 94V-0  |                  |

| MultiGig RT T2.8"<br>Full Center                 | J1[01-05]                                        | TE/ept         | 1410140-2 / 308-<br>50100-42 | 94V-0  |                  |

| MultiGig RT T2.8"<br>Full Center Rear w<br>1-8   | RJ0[01-05]                                       | TE/ept         | 1410965-2 / 308-<br>50102-42 | 94V-0  |                  |

| MultiGig RT T2.8"<br>Full Right                  | J2[01-05]                                        | TE/ept         | 1410142-2 / 308-<br>51100-42 | 94V-0  |                  |

| MultiGig RT T2.8"<br>Full Center Rear<br>w/o 1-8 | RJ0[01-05]                                       | TE/ept         | 1410966-2 / 308-<br>50103-42 | 94V-0  |                  |

| Description     | Reference | Vendor | Conn. P/N      | Rating | Mating Conn. P/N |

|-----------------|-----------|--------|----------------|--------|------------------|

| Aux Power (1x6) | P27       | Molex  | 22-11-2066     | 94V-0  | 22012061         |

| VBat (1x3)      | P26       | Molex  | 22-11-2036     | 94V-0  | 22012031         |

| NVMRO           | JP1       | Samtec | TSW-102-08-G-S | 94V-0  | Shunt            |

|                 |           |        |                |        |                  |

Crimps for P26, P27 - 8550102

Crimps for P1 - P5 - 500588100

Table 5-2: Backplane Connectors

The mating headers for P26 and P27 may not have a 1-to-1 pin alignment.

Document Part Number: 01A000128-A01

Issue Date: 15-May-2019

**Executive Member**

Pixus Technologies Inc. • 50 Bathurst Drive, Unit 6, Waterloo, Ontario Canada N2V 2C5 • (519) 885-5775 • www.pixustechnologies.com

Printed in Canada